I en era där beräkningsbehoven växer exponentiellt är optimerad verifiering inte längre en fördel – det är en förutsättning. Genom att accelerera utvecklingscykeln för AI/ML-SoC:er kan aktörer dramatiskt korta sin time-to-market och reducera kostnaderna, samtidigt som de säkrar den prestanda och energieffektivitet som morgondagens komplexa applikationer kräver. Snabbare och säkrare utveckling av AI SoC är kort sagt avgörande för att möta den växande efterfrågan på mer intelligenta, energieffektiva och pålitliga enheter, samtidigt som det är en ekonomisk nödvändighet för att hålla sig konkurrenskraftig.

Högpresterande verfirierings-lösningar ett måste

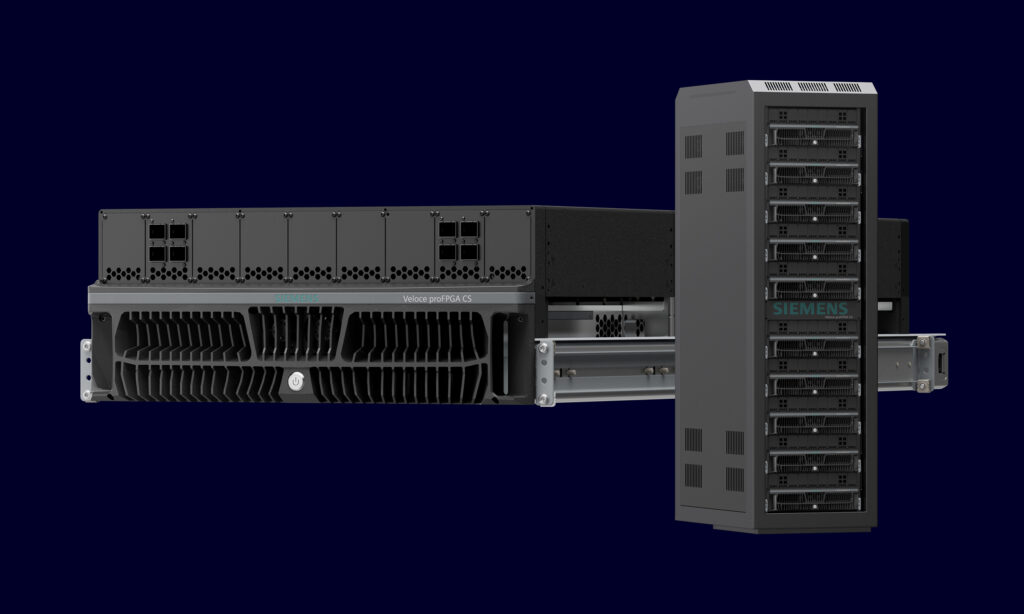

”I takt med att AI- och datorarkitekturer blir alltmer komplexa behöver halvledarteam högpresterande verifieringslösningar för att validera massiva arbetsbelastningar och snabba upp tiden till marknaden”, säger Narendra Konda, VP för hårdvaruteknik, NVIDIA. ”Integrationen av NVIDIAs prestandaoptimerade chiparkitekturer med Siemens Veloce proFPGA CS gör det möjligt för designers att fånga biljoner cykler på dagar, vilket ger den skala som behövs för att säkerställa tillförlitlighet för nästa generations AI.”

Prototypsystem baserade på FPGA (fältprogrammerbara grindmatriser) är snabba och låter användare köra pre-kiselverifierings-arbetsbelastningar på en bråkdel av den tid det skulle ta att köra samma arbetsbelastning i simulering eller till och med emulering. Dagens AI/ML-designer kräver dock ännu mer, delvis på grund av chipets komplexitet och delvis på grund av programvarans komplexitet.

För att skala till dessa branschkrav, uppfylla time-to-market och anpassa sig till tillförlitlighetskrav är förmågan att köra biljoner designcykler på kort tid nu avgörande. Traditionella verifieringsverktyg som simulering och emulering kan inte skalas upp längre än att köra miljontals, eller i bästa fall några miljarder cykler inom en rimlig och praktisk tidsram.

De centrala delarna i en pre-kiseldesigncykel

Slutligen några ord om pre-kiseldesigncykler (ofta kallat pre-silicon design cycles på engelska), som syftar på alla de utvecklingssteg som sker innan en integrerad krets eller ett chip fysiskt tillverkas i kisel.

Här är de centrala delarna i en pre-kiseldesigncykel:

- Arkitektur och specifikation: Man definierar vad chipet ska göra, dess prestandamål och vilka komponenter som behövs.

- RTL-design (Register Transfer Level): Designen skrivs i ett hårdvarubeskrivande språk (som Verilog eller VHDL). Det är här ”ritningen” av chipets logik skapas.

- Verifiering: Den mest tidskrävande fasen. Här används simuleringar för att testa att RTL-koden faktiskt gör vad den ska i alla tänkbara scenarier.

- Emulering och FPGA-prototyper: Man använder speciell hårdvara för att köra designen i hög hastighet (men fortfarande före tillverkning) för att kunna börja utveckla mjukvara och drivrutiner tidigt.

- Fysisk design (Layout): Den digitala logiken översätts till en fysisk karta över hur transistorer och ledningar ska placeras på kiselplattan.

- Sign-off: Den slutgiltiga kontrollen där man verifierar att designen möter alla tekniska krav (timing, strömförbrukning, tillverkningsbarhet) innan den skickas till fabriken (så kallad ”tape-out”).

Kort sagt är det den virtuella födelsen av ett chip där mjukvaruverktyg används för att garantera att hårdvaran fungerar perfekt när den väl blir verklighet.